Часть III. Вычислительные и аппаратные устройства

В этой части книги говорится о вычислительных и аппаратных устройствах сигнального процессора, к которым относятся арифметико-логическое устройство ALU, устройство умножения MAC, устройство сдвига, устройство обмена между шинами, программный автомат, генераторы адресов, таймер и синхронные последовательные порты. Дается описание архитектуры этих устройств и выполняемых с их помощью команд.

Глава 14. Устройство АЛУ

Назначение

Как уже говорилось ранее, процессор ADSP-2181 содержит три независимых вычислительных устройства (рис. 14.1). К их числу относятся: арифметико-логическое устройство (ALU), умножитель с накопителем (MAC) и устройство сдвига (SHIFTER). Эти устройства работают с 16-разрядными данными и имеют аппаратную поддержку обмена данными, позволяющую обеспечить многопоточность.

Рис. 14.1. Процессор ADSP-2181

Арифметико-логическое устройство выполняет ряд стандартных арифметических и логических команд. MAC выполняет одноцикловые операции умножения, умножения-сложения и умножения-вычитания. SHIFTER осуществляет логические и арифметические сдвиги, нормализацию, денормализацию и операцию получения порядка, а также управление форматом данных, разрешая работу с плавающей точкой.

Вычислительные модули размещаются последовательно друг за другом таким образом, чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы вычислительных устройств собираются на 16-разрядную шину R-BUS.

Все три устройства содержат входные и выходные регистры, которые доступны через 16-разрядную шину данных. Команды, выполняемые в устройствах, берут в качестве операндов данные, находящиеся в регистрах ввода, и после выполнения операции записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. Шина R-BUS позволяет результату одного вычисления стать операндом для другой операции. Это экономит время благодаря исключению лишних пересылок данных между устройствами и памятью.

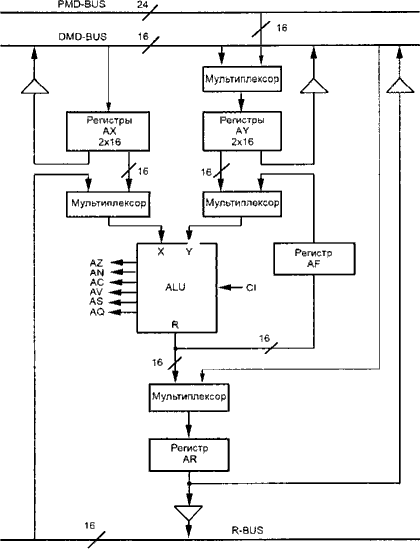

Рассмотрим подробнее ALU. Его структурная схема приведена на рис. 14.2.

Рис. 14.2. Структурная схема ALU

Арифметико-логическое устройство является 16-разрядным устройством с двумя 16-разрядными входными портами данных X и Y и одним выходным портом результата R. ALU генерирует шесть сигналов состояния: ноль (AZ), негатив (AN), перенос (AC), переполнение (AV), знак (AS) и частное (AQ). В конце каждого цикла процессора эти сигналы сохраняются в регистре состояния процессора ASTAT. Описание назначения этих сигналов состояния приведено в табл. 14.1.

Таблица 14.1 Описание назначения сигналов состояния

| Сигнал | Расшифровка | Назначение |

|---|---|---|

| AZ | ZERO (НОЛЬ) | Разряд нулевого результата. Устанавливается в 1, если результат операции равен нулю. Является результатом логического сложения всех битов регистра результатов ALU |

| AN | NEGATIV (НЕГАТИВ) | Знаковый разряд результата ALU. Устанавливается в 1, если результат отрицательный |

| AV | OVERFLOW (ПЕРЕПОЛНЕНИЕ) | Разряд переполнения. Устанавливается в 1, если происходит переполнение ALU путем переноса 1 в знаковый разряд при сложении чисел |

| AC | CARRY (ПЕРЕНОС) | Разряд переноса. Устанавливается в 1 при сложении беззнаковых чисел, если происходит переполнение ALU путем переноса 1 из старшего разряда |

| AS | SIGN (ЗНАК) | Знаковый разряд. Определяется при операции вычисления абсолютного значения числа ABS. Устанавливается в 1, если операнд имеет отрицательное значение |

| AQ | QUOTIENT (ЧАСТНОЕ) | Разряд состояния частного. Формируется только командами DIVS и DIVQ |

Порт ввода X может принимать данные от двух источников: из блока регистров АХ или с шины результата R-BUS. Шина R-BUS обеспечивает обмен данными между всеми вычислительными устройствами. Блок регистров АХ состоит из двух регистров: AX0 и AX1. Эти регистры подключены к шине памяти данных DMD-BUS. Система команд позволяет читать содержимое регистра АХ и на шину памяти программ PMD-BUS, для этого используется устройство обмена между шинами. Выводы регистров AX0 и AX1 реализованы таким образом, чтобы один из них служил операндом для ALU, а другой в это время мог считываться на шину DMD-BUS.

Порт ввода Y также принимает данные от двух источников: из блока регистров AY и регистра обратной связи AF. Блок регистров AY состоит из двух регистров AY0 и AY1. Эти регистры доступны для чтения и записи с шиной DMD-BUS. Система команд процессора позволяет читать регистры AY0 и AY1 с помощью шины PMD-BUS, но также с использованием устройства обмена между шинами. Выводы регистров AY0 и AY1 реализованы аналогично регистрам AX0 и AX1.

Выход ALU подключен к выходному регистру результата AR и через регистр обратной связи AF на вход ALU через мультиплексор. Регистр AF позволяет результату вычисления использоваться в качестве следующего операнда. Регистр AR имеет выход на шину DMD-BUS и R-BUS. В системе команд предусмотрена возможность чтения регистра AR посредством шины PMD-BUS аналогично двум предыдущим вариантам.

Любой из регистров ALU доступен для записи и чтения в течение цикла процессора (для чтения — в начале цикла, и для записи - в конце процессорного цикла). Таким образом, новое значение, записанное в конце одного цикла, может быть прочитано лишь в начале следующего. Это позволяет входным регистрам записать в ALU операнд в начале цикла и считать следующий операнд в конце того же цикла. Это также позволяет сохранить содержимое регистра результата в памяти и оперировать со следующим результатом в одном цикле.

Арифметико-логическое устройство имеет альтернативные (теневые) банки регистров AX, AY, AF и AR. На структурной схеме они изображены в виде теней. В конкретный момент времени доступен только один из типов банков. Дополнительный банк может быть использован для автоматического сохранения данных в регистрах ALU при быстром переключении на выполнение подпрограммы. В этом случае экономится время на сохранение текущих данных в памяти процессора.

Выбор главного или альтернативного банка регистров определяется битом 0 регистра режимов процессора MSTAT. Если этот разряд равен 0, то выбран главный банк, если он равен 1, то выбирается дополнительный банк.

Арифметико-логическое устройство выполняет набор стандартных арифметических и логических операций. Из арифметических операций АЛУ выполняет сложение, вычитание, отрицание, инкремент, декремент и вычисление модуля. Эти операции дополнены двумя примитивами деления, с помощью которых возможна реализация цикла многократного деления. Из логических операций АЛУ выполняет логическое сложение (OR), логическое умножение (AND), исключающее ИЛИ (XOR), и логическое отрицание (NOT). Стандартные операции ALU приведены в табл. 14.2.

Таблица 14.2 Стандартные операции ALU

| Операция | Назначение |

|---|---|

| R=X+Y | Сложение операндов X и Y |

| R=X+Y+CI | Сложение операндов X и Y с переносом |

| R=X-Y | Вычитание операнда Y из X |

| R=Y-X | Вычитание операнда X из Y |

| R=X-Y+CI-1 | Вычитание операнда Y из X с заемом |

| R=Y-X+CI-1 | Вычитание операнда X из Y с заемом |

| R= -X | Инверсия операнда X |

| R= -Y | Инверсия операнда Y |

| R=X+1 | Инкремент операнда X |

| R=Y+1 | Инкремент операнда Y |

| R=X-1 | Декремент операнда X |

| R=Y-1 | Декремент операнда Y |

| R=PASS X | Результат равен операнду X с установкой флагов регистра статуса ASTAT |

| R=PASS Y | Результат равен операнду Y с установкой флагов регистра статуса ASTAT |

| R=0 | Очистка результата |

| R=ABS X | Результат равен абсолютному значению операнда X (значение по модулю) |

| R=X AND Y | Логическое умножение операндов X и Y |

| R=X OR Y | Логическое сложение операндов X и Y |

| R=X XOR Y | Исключающее «ИЛИ» операндов X и Y |

| R=NOT X | Логическое отрицание X |

| R=NOT Y | Логическое отрицание Y |

В качестве условных записей операндов X, Y и R ALU, указанных в табл. 14.2, могут выступать следующие регистры:

- для X: AX0, АХ1, AR, MR0, MR1, MR2, SR0, SR1;

- для Y: AY0, AY1, AF;

- для R: AR и AF.

Регистры MR0, MR1, MR2 принадлежат умножителю MAC, а регистры SR0, SR1 устройству сдвига Shifter. Они доступны ALU по шине данных.

С целью обработки чисел с повышенной точностью, в ALU используются сигнал переноса CI (carry-in) и бит переноса AC (ALU carry). Операция сложения с переносом предназначена для сложения старших частей чисел, а операция вычитания с заемом — для их вычитания.

Регистр AR может работать в режиме насыщения. В этом режиме он принимает максимально возможное отрицательное или положительное значение, если операция заканчивается переполнением. Эта функция регистра AR становится возможной при установке в единицу разряда 3 регистра MSTAT. В табл. 14.3 показано содержимое регистра AR ALU в зависимости от флагов регистра состояния ASTAT при включенном, с помощью регистра MSTAT, режиме насыщения.

Таблица 14.3 Содержимое регистра AR ALU в зависимости от флагов регистра состояния

| AV (переполнение) | АС (перенос) | Содержимое AR |

|---|---|---|

| 0 | 0 | В соответствии с результатом ALU |

| 0 | 1 | В соответствии с результатом ALU |

| 1 | 0 | 0111111111111111 (максимальное положительное число) |

| 1 | 1 | 1000000000000000 (минимальное отрицательное число) |

Режим блокировки переполнения ALU разрешается при установке в единицу бита 2 регистра MSTAT. В этом режиме при переполнении ALU разряд AV устанавливается в единицу и при последующих операциях остается в этом состоянии. Таким образом, последующее переполнения уже не генерируются. Бит состояния AV можно очистить непосредственно с DMD шины путем записи в регистр состояния ASTAT нуля.

Арифметико-логическое устройство поддерживает операции деления. Деление осуществляется путем сложения и циклического сдвига чисел с помощью двух специальных примитивов деления DIVS и DIVQ. Команда DIVS вычисляет знаковый бит частного, а DIVQ вычисляет один бит частного. Данные команды применяются для деления знаковых или беззнаковых чисел. Алгоритм деления выполняет либо сложение, либо вычитание, основываясь на знаках делителя и частичного остатка. Остаток при этих операциях недоступен. При этом делитель и делимое должны быть одного типа. Обычная точность деления для 32-разрядного делимого, 16-разрядного делителя и 16-разрядного остатка реализуется за 16 циклов. Делитель может быть сохранен в регистре AX0, АХ1 или в любом регистре результатов R. Старший байт знакового делителя должен находиться либо в регистре AY1, либо в AF, а беззнакового делителя — в регистре AF. Младший байт делителя любого типа должен находиться в AY0. Остаток после деления будет записан в регистр AY0.

Первый из двух примитивов — это команда DIVS (деление-знак). Она предназначена для деления чисел со знаком. Структура операции DIVS показана на рис. 14.3.

Рис. 14.3. Структура операции DIVS

Данная операция вычисляет знаковый бит остатка, выполняя операцию «ИСКЛЮЧАЮЩЕЕ ИЛИ» для знаковых разрядов делителя и делимого.

Регистр AY0 сдвигается на одну позицию таким образом, чтобы знаковый разряд переместился в позицию LSB. Вычисленный знаковый разряд сохраняется в бит AQ регистра состояния. При делении чисел без знака операция DIVS не применяется. В этом случае бит AQ устанавливается в 0. Он показывает, что остаток должен быть положительным.

Второй примитив деления — это команда DIVQ (деление-частное), которая выполняется многократно и генерирует по одному биту частного после очередного выполнения. При простой точности деления чисел без знака команда DIVQ выполняется 16 раз, для такой же точности деления чисел со знаком операция выполняется 15 раз после вычисления знакового разряда с помощью команды DIVS. Операция DIVQ проиллюстрирована на рис. 14.4. DIVQ сдвигает регистр AY0 влево на один разряд так, чтобы новый бит частного оказался в позиции младшего разряда (LSB). Состояние бита AQ, которое генерируется предыдущей операцией, определяет операцию ALU для вычисления частичного результата. Если AQ=1, то ALU добавляет делитель к частичному результату в AF. Если AQ=0, то ALU вычитает делитель из частичного результата в AF. Так же как и в операции DIVS, ALU выводит результат в регистр AF. Формат результата при любом числовом представлении определяется форматом делителя и делимого.

Рис. 14.4. Операция DIVQ

Пусть NL — число разрядов влево и NR — число разрядов вправо от двоичной точки делимого, DL и DR — соответственно то же самое, только для делителя. Тогда частное состоит из NL-DL+1 битов слева от двоичной точки и содержит NR-DR-1 битов справа. Ниже показан пример формата чисел при выполнении операции деления.

Делимое: XXXXX.XXXXXXXXXXXXXXXXXXXXXXXXXXXX

NL=5 бит NR=27 бит

Делитель: XX.XXXXXXXXXXXXXX

DL=2 бит DR=14 бит

Частное: XXXX.XXXXXXXXXXXX

(NL-DL+1)=4 бит (NR-DR-1)=12 бит

Иногда необходимо некоторое изменение формата делимого и делителя. Например, если оба операнда знаковые и дробные (делимое в формате 1.31, а делитель в формате 1.15), то результат запишется в формате 1.15. Таким образом, для получения правильного результата операции деления необходимо, чтобы делимое было меньше делителя.

Чтобы разделить два целых числа (делимое в формате 32, а делитель в формате 16), необходимо перед делением привести делимое к формату 31, т.е. сдвинуть его влево на один разряд. Если результат не может быть представлен в формате частного, как сказано выше, или когда делитель равен нулю или меньше делимого по абсолютному значению, происходит переполнение.

При реализации алгоритма деления для знаковых операндов делитель должен храниться в AX0 и AX1 или в любом регистре с шины R. Старшее слово делимого может быть загружено в AY1 или AF, и младшее слово делимого загружается в AY0. Чтобы вычислить частное, сначала выполняется команда DIVS, которая вычисляет знак частного, за которой следуют 15 команд DIVQ, для вычисления 15 бит частного. Пример подпрограммы знакового деления с фиксированной точкой показан ниже. Эта подпрограмма берет делитель из регистра AX0, старшее слово делимого из AF и младшее слово делимого из AY0. Частное возвращается в AY0.

.MODULE Sig_Div_FP; { Входные данные: AF = старшее слово делимого AY0 = младшее слово делимого AX0 = 16-битный делитель Выходные данные: AY0 = 16-битный результат Изменяемые регистры: AY0, AF Время вычисления=17 циклов}.ENTRY sdivfp;sdivfp: DIVS AF, AX0; {Вычисление знакового бита}DIVQ AX0; DIVQ AX0; DIVQ AX0; {Вычисление 15 бит частного}DIVQ AX0; DIVQ AX0; DIVQ AX0;DIVQ AX0; DIVQ AX0; DIVQ AX0;DIVQ AX0; DIVQ AX0; DIVQ AX0;DIVQ AX0; DIVQ AX0; DIVQ AX0;RTS;.ENDMOD;Ниже приводится полный список команд ALU в соответствии с принятыми ранее условными сокращениями. Назначение команд очевидно из их записи и комментариев для некоторых из команд. Команды сложения и сложения с переносом:

[IF cond] |AR| = xop + |yop |; |AF| |C | |yop + C | |constant|Команды вычитания и вычитания с займом:

[IF cond] |AR| = xop - |yop |; |AF| |yop+С-1 | |constant|[IF cond] |AR| = yop - |xop |; |AF| |xop+C-1 | |constant|Команды логических операций И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ:

[IF cond] |AR| = xop |AND| yop; |AF| |OR | |XOR|Команды передачи:[IF cond] |AR| = PASS|xop |; |AF| |yop | |constant|Команды смены знака:

[IF cond] |AR| = - |xop|; |AF| |yop|Команды логического отрицания HE:

[IF cond] |AR| = NOT |xop|; |AF| |yop| |0 |Команды вычисления абсолютного значения:

[IF cond] |AR| = ABS |xop|; |AF|Команды инкремента:

[IF cond] |AR| = |yop+1|; |AF|Команды декремента:

[IF cond] |AR| = |yop-1|; |AF|Команды битовых операций:

[IF cond] |AR| = |TSTBIT n xop|; {операция логического «И» разряда n с 1} |SETBIT n xop|; {операция установки разряда n в 1} |CLBIT n xop|; {операция установки разряда n в 0} |TGBIT n xop|; {операция «ИСКЛЮЧАЮЩЕЕ ИЛИ» бита n с 1}Здесь n могут принимать значения от 0 до 15

Команды поразрядного деления:

[IF cond] |AR| = DIVS yop, xop;[IF cond] |AR| = DIVQ xop;Команды тестирования результата:

NONE = ; Последняя команда выполняет заданную команду АЛУ, устанавливает флаги и сбрасывает значение результата. Она позволяет тестировать значения в регистрах без изменения содержимого AR или AF. Строка

Для всех приведенных выше команд ALU разрешено использовать следующие операнды:

xop: AX0, АХ1, AR, MR0, MR1, MR2, SR0, SR1; yop: AY0, AY1, AF;

constant: 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32767, -2, -3, -5, -9, -17, -33, -65, -129, -257, -513, -1025, -2049, -4097, -8193, -16385, -32768.

Команда DIVS не может использовать регистр AY0 как оператор yop. Коды условия IF соответствуют кодам, приведенным ранее в табличном виде.

Примеры записи команд:

AR=AX0+AY0+C; /* Присвоить регистру AR значение суммы регистров AX0, AY0 и переноса*/IF EQ AR=AX0+AY0+C; /* Выполнение описанной выше операции при условии равенства нулю предыдущего результата */AF=TSTBIT 7 AX; /* Занести в регистр AF значение результата операции логического «И» разряда 7 с единицей */

Глава 15. Устройство MAC

В этой главе говорится о вычислительном устройстве MAC (умножителя с накопителем) сигнального процессора и выполняемых в нем командах.

Структура устройства MAC

В этой главе говорится о вычислительном устройстве MAC (умножителя с накопителем) сигнального процессора и выполняемых в нем командах.

Свое название устройство MAC получило от сокращения английских слов: multiplier (умножитель) и accumulator (накопитель). Устройство MAC выполняет быстрые одноцикловые операции умножения, умножения с добавлением, умножения с вычитанием, функции насыщения и очистку результата. Функция обратной связи позволяет части результата в одном цикле быть одним из сомножителей в следующем цикле.

Операции в MAC производятся над числами, представленными в виде двоичных последовательностей. Результат выдается в том же виде.

Процессор ADSP-2181 поддерживает два режима корректировки формата: дробный режим для дробных операндов формата 1.15 и целочисленный режим для целых чисел формата 16.0.

Когда процессор умножает два операнда в формате 1.15, в результате получается число в формате 2.30 (два знаковых и 30 дробных разрядов).

В дробном режиме MAC автоматически сдвигает результат на один бит влево перед пересылкой его в регистр результата MR. Этим сдвигом результат приводится к виду 1.31, который может быть округлен до формата 1.15.

В целочисленном режиме сдвига влево не происходит. Например, при умножении операндов в формате 16.0 результат представляется в виде 32.0.

Сдвиг влево в этом случае не нужен, т.к. он изменит числовое представление результата. В табл. 15.1 показаны форматы данных операндов и результата для вычислительных устройств процессора ADSP-2181.

Таблица 15.1 Форматы данных операндов и результата для вычислительных устройств процессора ADSP-2181

| Операции | Арифметические форматы | |

|---|---|---|

| Операнды | Результат | |

| Устройство ALU | ||

| Сложение | Знаковые числа или без знака | Установка флагов |

| Вычитание | Знаковые числа или без знака | Установка флагов |

| Логические операции | Двоичные строки | Тот же, что и операнды |

| Деление | Знаковые числа или без знака | Тот же, что и операнды |

| Переполнение ALU | Знаковые числа | Тот же, что и операнды |

| Бит коррекции ALU | 16-разрядные числа без знака | Тот же, что и операнды |

| Насыщение ALU | Знаковые числа | Тот же, что и операнды |

| Устройство MAC (дробные числа) | ||

| Умножение (P) | 1.15 знаковые числа /без знака | 32 разряда (2.30) |

| Умножение (MR) | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Умножение с накоплением | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Умножение с вычитанием | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Насыщение MAC | Знаковые числа | Тот же, что и операнды |

| Устройство MAC (целые числа) | ||

| Умножение (P) | 1.15 знаковые числа /без знака | 32 разряда (32.0) |

| Умножение (MR) | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Умножение с накоплением | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Умножение с вычитанием | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Насыщение MAC | Знаковые числа | Тот же, что и операнды |

| Устройство сдвига Shifter | ||

| Логические сдвиги | Баз знака/двоичные строки | Тот же, что и операнды |

| Арифметические сдвиги | Знаковые числа | Тот же, что и операнды |

| Определение порядка | Знаковые числа | Тот же, что и операнды |

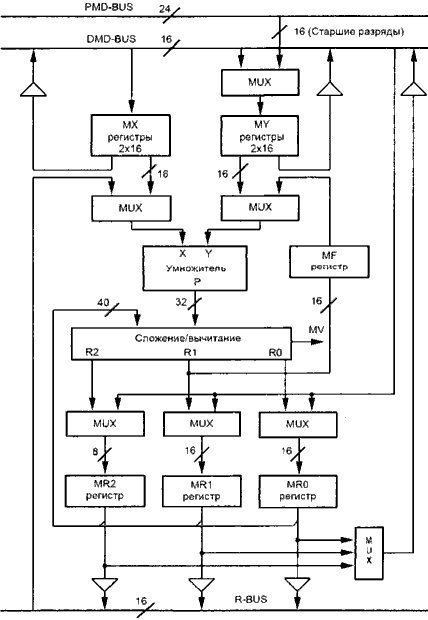

Рассмотрим подробнее содержимое устройства MAC. Его структурная схема приведена на рис. 15.1.

Рис. 15.1. Структурная схема MAC

MAC имеет два входных 16-разрядных порта X и Y и один 32-разрядный порт вывода результата P. 32-разрядный результат поступает в 40-разрядный блок сложения/вычитания, который либо прибавляет, либо вычитает текущий результат из регистра результата MR, либо передает текущий результат непосредственно в MR. Регистр MR имеет 40 разрядов. Фактически регистр MR состоит из трех регистров. Два из них, MR0 и MR1, являются 16-разрядными, а регистр MR2 8-разрядный. Мультиплексоры MUX позволяют коммутировать внутри устройства один из нескольких операндов.

Блок сложения/вычитания имеет более 32 разрядов для того, чтобы учесть промежуточные переполнения в ряде операций умножения с накоплением. Флаг MV (переполнение) устанавливается в единицу, если значение аккумулятора превышает 32 разряда.

Регистры ввода-вывода подобны регистрам ALU. Порт X может принимать данные из регистра MX или из любого другого регистра на R-шине результата. R-шина соединяет выходные регистры всех вычислительных модулей для непосредственного использования результатов вычислений в качестве входных операндов. Регистр MX состоит из двух регистров (MX0 и MX1).

Эти регистры читаются и записываются с DMD-шины. Организованы регистры MX0 и MX1 таким образом, что один из них поставляет множитель в блок умножения, а другой управляет DMD-шиной.

Порт Y принимает данные из регистра MY или регистра обратной связи MF. Регистр MY также разбит на два регистра (MY0 и MY1), доступ к которым осуществляется с DMD-шины и возможна запись с PMD-шины. Система команд предусматривает чтение этих регистров с помощью PMD-шины, но прямого доступа для этой операции нет, в этом случае используется устройство DMD-PMD обмена. Выводы регистра MY устроены аналогично MX.

Результат умножения поступает либо в блок сложения/вычитания, либо в регистры MY или MF. Регистр обратной связи MF позволяет результату вычисления в предыдущем цикле становиться операндом умножения на входе Y, в последующей операции. 40-разрядный регистр MR разделен на три регистра (MR0, MR1, MR2). Содержимое любого из них может быть выведено на DMD-шину или R-шину и записано с DMD-шины.

Любой из регистров MAC может быть прочитан и записан в одном цикле. Чтение данных происходит в начале цикла, а запись - в конце цикла. Прочитанное содержимое регистра в начале одного цикла записывается в конце предыдущего, следовательно, новое значение регистра может быть прочитано только в течение следующего цикла. Такой механизм позволяет входному порту предоставлять операнд для MAC в начале цикла и оперировать со следующим значением из памяти в конце того же цикла. Это относится и к выходному регистру.

Регистры MR, MF, MX, MY продублированы в теневых банках. Одновременно процессору может быть доступен лишь один из банков. Теневой банк регистров может быть активизирован для чрезвычайно быстрого контекстного переключения. Таким образом, новая задача, типа подпрограммы обработки прерывания, может выполняться без сохранения текущих данных в памяти, благодаря использованию теневых банков. Выбор первичного или теневого банка регистров определяется установкой нулевого разряда в регистре MSTAT состояний процессора. Если этот разряд установлен в 0, то выбран первичный банк.

Теперь рассмотрим операции вычислительного устройства MAC, входные форматы данных, обработку переполнения и насыщения.

Набор стандартных операций MAC приведен в табл. 15.2.

Таблица 15.2 Набор стандартных операций MAC

| Операция | Назначение |

|---|---|

| X*Y | Умножение X на Y |

| MR+X*Y | Умножение X на Y и сложение с MR |

| MR-X*Y | Умножение X на Y и вычитание из MR |

| 0 | Очистка MR |

Как было сказано выше, сигнальный процессор ADSP-2181 обеспечивает два режима работы операций умножения с накоплением. Первый из них — режим работы с дробными числами в формате 1.15. Второй — режим работы с целыми числами в формате 16.0.

В дробном режиме выходной регистр P корректирует формат, т.е. прежде чем добавить значение в MR, оно сдвигается на один разряд влево. Таким образом, бит 31 регистра P запишется в 32-й разряд регистра MR, а 0-й разряд — в первый. В позицию младшего разряда (LSB) при этом записывается ноль. На рис. 15.2 показан дробный формат работы модуля умножения.

Рис. 15.2. Дробный формат работы модуля умножения

В целочисленном формате (рис. 15.3) регистр P не сдвигается, прежде чем прибавиться к MR.

Рис. 15.3. Целочисленный формат

Выбор режима осуществляется установкой 4-го разряда регистра MSTAT процессора. Если этот разряд установлен в 1, то выбран целочисленный режим. В любом формате блок умножения формирует 32-разрядный результат и передает его в блок сложения/вычитания, где получается конечное значение операции, которое записывается в MR.

В операциях MAC обрабатываются данные, которые поступают на порты X и Y, а результат операций выводится на шину R. Ниже приведен перечень регистров, доступных для этих портов.

Регистры для входного порта X — MX0, МХ1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для входного порта Y — MY0, MY1, MF.

Регистры для выходного порта R — MR (MR0, MR1, MR2), MF.

Для облегчения умножения входные операнды могут находиться в любых форматах. Входные форматы определяются как часть команды и выбираются динамически при обращении к блоку умножения.

Формат: «знаковый * знаковый» — используется при умножении двух знаковых чисел простой точности или двух старших частей знаковых чисел двойной точности.

Формат: «без знака * знаковый» или «знаковый * без знака» — используется при умножении верхней части знакового числа на нижнюю часть другого или для умножения знакового числа простой точности с числом той же точности без знака.

Формат: «без знака * без знака» — используется при умножении чисел простой точности без знака или нижних частей знаковых чисел двойной точности.

Как показано на рис. 15.1, регистр MR разбит на три регистра: MR0 (биты 0-15), MR1 (биты 16-31) и MR2 (биты 32-39). Каждый из этих регистров может быть загружен с DMD-шины и выведен на R-шину или DMD-шину. Регистр MR2 связан с младшими восемью разрядами этих шин. Во время передачи данных MR2 на R-шину или DMD-шину происходит добавление 8 знаковых разрядов для расширения числа до 16 разрядов. Кроме того, при загрузке данных с DMD-шины в регистр MR1 регистр MR2 служит как добавление регистра MR1, и заполняется значением старшего знакового разряда MR1. Для того чтобы загрузить в регистр MR2 данные, отличные от знакового разряда MR1, необходимо загружать MR2 после загрузки MR1. Загрузка регистра MR0 не влияет на регистры MR0 и MR1.

После каждой операции блок сложения/вычитания генерирует сигнал переполнения MV, который подключен к регистру состояния арифметики процессора ASTAT. Бит MV устанавливается в единицу, если результат сложения выходит за границы регистров MR1/MR2 — 32 бита, т.е. если все девять старших разрядов регистра MR одновременно не нули или не единицы.

Регистр MR имеет возможность насыщения в определенном положительном или отрицательном значении, если происходит переполнение. Насыщение зависит от состояния бита MV регистра состояний арифметики ASTAT и бита MSB регистра MR2. Операцию насыщения описывает табл. 15.3.

Таблица 15.3 Описание операции насыщения

| Флаг MV | Старший разряд MR2 | Содержимое регистра MR после операции |

|---|---|---|

| 0 | 0 или 1 | Без изменений |

| 1 | 0 | 00000000 0111111111111111 1111111111111111 (положительное) |

| 1 | 1 | 11111111 1000000000000000 0000000000000000 (отрицательное) |

Насыщение в MAC является скорее командой, чем режимом, как в ALU. Она используется при завершении последовательности умножений с накоплением, таким образом, чтобы промежуточные переполнения не привели сумматор к насыщению.

Переполнение больше старшего разряда MSB недопустимо. В обратном случае знаковый разряд будет потерян, и насыщение не будет правильным. Однако, чтобы достигнуть этого состояния, требуется 255 циклов переполнения.

В сумматоре MAC можно округлять 40-разрядный результат на границе между 15-м и 16-м разрядами. Округление относится к системе команд процессора. Округленный результат направляется либо в регистр MR, либо в регистр обратной связи MF. Когда для вывода используется MF, в него записывается 16-разрядный округленный результат. Аналогично, если для вывода выбран MR, то в MR1 записываются 16 разрядов округленного результата, а в регистр MR2 результат округления, таким образом, получается 24-разрядный округленный результат.

Сумматор производит процедуру округления без смещения. Стандартный метод смещенного округления состоит в записи единицы в 15-й разряд. Этот метод вызывает положительное смещение, так как срединное значение числа, когда MR=0x8000 округляется в сторону увеличения. Сумматор устраняет это смещение, принудительно устанавливая шестнадцатый разряд в ноль, когда значение регистра MR достигает середины. При этом четные значения MR1 округляются в сторону уменьшения, а нечетные в сторону увеличения. Таким образом достигается нулевое смещение при выборе множества равномерно распределенных значений. Для наглядности сказанного выше, в табл. 15.4 приведено два примера операций округления результата.

Таблица 15.4 Примеры операций округления результата

| Операнды и операции | Регистры | ||

|---|---|---|---|

| MR2 | MR1 | MR0 | |

| Пример 1 | |||

| Неокругленное значение, где 15-й разряд равен 1 | xxxxxxxx | xxxxxxxx 00100101 | 1xxxxxxxxxxxxxxx |

| Прибавление 1 к 15-му разряду и учет переноса | 100000000 0000000 | ||

| Округленное значение | xxxxxxxx | хххххххх 00100110 | 0xxxxxxxxxxxxxxx |

| Пример 2 | |||

| Неокругленное значение, где 15-й разряд равен 1, а разряды с 0-го по 14-й равны нулю | xxxxxxxx | хххххххх 00100110 | 100000000 0000000 |

| Прибавление 1 к 15-му разряду и учет переноса | 100000000 0000000 | ||

| Неокругленное значение, где бит 16 равен 1 | xxxxxxxx | хххххххх 00100111 | 00000000 00000000 |

| Установка 16-го разряда в ноль и получение округленного значения | xxxxxxxx | хххххххх 00100110 | 00000000 00000000 |

x — произвольное значение (0 или 1).

В первом примере число не является срединным и производится его стандартное округление.

Во втором примере число имеет срединное значение, поэтому его 16-й разряд устанавливается в ноль. Алгоритм округления применяется для каждой операции округления, но становится очевидным лишь при таком наборе младших бит, который показан в примере 2.

В процессорах ADSP-2181 возможен режим смещенного округления. Этот режим выбирается путем установки 12-го бита (BIARND) регистра управления SPORT0. Если BIARND=0, то используется операция несмещенного округления, если BIARND=1, то смещенного. Примеры таких операций приведены в табл. 15.5.

Таблица 15.5 Примеры операций округления

| Значение регистра MR до округления | Результат округления со смещением | Результат округления без смещения |

|---|---|---|

| 00-0000-8000 | 00-0001-8000 | 00-0000-8000 |

| 00-0001-8000 | 00-0002-8000 | 00-0002-8000 |

| 00-0000-8001 | 00-0001-8001 | 00-0001-8001 |

| 00-0001-8001 | 00-0002-8001 | 00-0002-8001 |

| 00-0000-7FFF | 00-0000-7FFF | 00-0000-7FFF |

| 00-0001-7FFF | 00-0001-7FFF | 00-0001-7FFF |

Этот режим действует только в том случае, когда значение регистра MR0 больше 0x8000. Во всех других случаях работают обычные операции округления. Этот режим позволяет более эффективно реализовывать алгоритмы, использующие смещенное округление, например подпрограммы речевого сжатия GSM.

Ниже приводится полный список команд устройства умножителя-накопителя MAC, также в соответствии с принятыми ранее условными сокращениями. Назначение команд приводится в тексте описания этих команд и комментариях для некоторых из команд.

Команды умножения:

[IF cond] |MR| = xop * |yop| |(SS) |; |MF| |xop| |(SU) | |(US) | |(UU) | |(RND)|Здесь присутствуют новые символы, которые имеют следующее назначение:

S — входной операнд xop или yop знаковый;

U — входной операнд xop или yop беззнаковый;

RND — выходное значение округляется.

Например, команда:

MR=MX0*MY0(SU);означает, что в регистр MR будет занесен результат умножения знакового значения из регистра MX0 на беззнаковое значение из регистра MY0.

Команда:

MR=SR1 *MY0(RND);означает, что в регистр MR будет занесен результат умножения значения из регистра SR1 на значение из регистра MY0 и результат вычисления будет округлен.

Команды умножения с накоплением:

[IF cond] |MR| = MR + xop * |yop| |(SS) |; |MF| |xop| |(SU) | |(US) | |(UU) | |(RND)|Пример:

MR=MR+MX0*MY0 (SS);Здесь в регистр MR будет занесен результат сложения предыдущего значения регистра MR с результатом умножения знакового значения из регистра MX0 на знаковое значение из регистра MY0.

Команды умножения с вычитанием:

[IF cond] |MR| = MR - xop * |yop| |(SS) |; |MF| |xop| |(SU) | |(US) | |(UU) | |(RND)|Команды пересылки MR:

[IF cond] |MR| = MR |(RND)|; |MF|Фактически эти команды осуществляют пересылку содержимого регистра MR в регистр MR или в регистр MF с округлением значения.

Команды очистки:

[IF cond] |MR| = 0; |MF|Команда условного насыщения регистра MR:

IF MV SAT MR;Здесь MV — код условия переполнения умножителя.

Для всех команд MAC разрешено использовать следующие операнды:

xop: MX0, МХ1, AR, MR0, MR1, MR2, SR0, SR1;

yop: MY0, MY1, MF;

Коды условия IF соответствуют кодам, приведенным ранее в табличном виде.

Примеры записи команд:

MR=MR+MX0*MY0(SS); /* Присвоить регистру MR значение суммы регистров MR и произведения MX0 на MY0, где оба операнда произведения знаковые*/MF=AR*MY0(RND) /* Присвоить регистру MF значение произведения регистра AR на MY0, с округлением результата*/MF=AR*MY0(RND), MY1=DM(I3,M3); /* Мультипроцессорная команда вычисления произведения и одновременной пересылки данных из памяти в регистр*/MF=MR(RND); /* Осуществить пересылку содержимого регистра MR в регистр MF с округлением значения */IF EQ MR=0; /* Очистить регистр MR, если предыдущий результат равен нулю */

Глава 16. Устройство сдвига

В этой главе говорится об устройстве сдвига сигнального процессора и выполняемых с его помощью командах.

В этой главе говорится об устройстве сдвига сигнального процессора и выполняемых с его помощью командах.

Устройство сдвига именуется как Shifter и обеспечивает полный набор сдвиговых функций для 16-разрядных операндов, результатом которых является 32-разрядное слово данных. К числу сдвиговых функций относятся арифметические сдвиги, логические сдвиги и нормализация. Кроме того, shifter позволяет вычислить порядок (экспоненту) числа и порядок для целого массива (блока) чисел. Эти базовые функции могут быть объединены для быстрого преобразования любого формата чисел, в том числе и чисел с плавающей точкой.

На рис. 16.1 представлена структурная схема устройства сдвига. Shifter включает в себя следующие основные блоки: массив сдвига, логику OR/PASS (ИЛИ/ПЕРЕДАЧА), детектор порядка и логику сравнения порядка.

Рис. 16.1. Структурная схема устройства сдвига

Массив сдвига состоит из шестнадцати 32-разрядных регистров. Он принимает 16-разрядные данные и в одном цикле может поместить их в любой позиции 32-разрядного поля вывода, начиная с данных, полностью сдвинутых влево, и кончая данными, полностью сдвинутыми вправо, за один цикл. Это дает 49 вариантов возможных размещений 16-разрядных входных данных в 32- разрядном поле вывода, как показано в табл. 16.1.

Таблица 16.1 Варианты возможных размещений 16-разрядных входных данных в 32-разрядном поле вывода

| N | Разряды | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 2 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 |

| 3 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 |

| … | ||||||||||||||||||||||||||||||||

| 17 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 18 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X |

| … | ||||||||||||||||||||||||||||||||

| 33 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 34 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| … | ||||||||||||||||||||||||||||||||

| 47 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 48 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 49 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | Z | X | X | X |

Размещение 16 входных разрядов определяется кодом управления «С» и сигналом ссылки HI/LO. Код управления «С» является 8-битным значением, которое указывает направление сдвига и число разрядов, на которое необходимо будет сдвинуть данные.

Положительные значения кода управления указывают на сдвиг данных влево, а отрицательные на сдвиг вправо. Код управления может быть взят из регистра экспоненты SE или непосредственно из инструкции команды. Сигнал ссылки HI/LO определяет начальную точку сдвига. В состоянии HI все сдвиги производятся относительно регистра SR1 (старшей половины выходных данных), а в состоянии LO все сдвиги производятся относительно регистра SR0 (младшей половины выходных данных). В табл. 16.2 показаны все возможные комбинации сдвигов данных для сигналов ссылки LO и HI.

Таблица 16.2 Возможные комбинации сдвигов данных для сигналов ссылки L0 и HI

| Управляющий код для сигнала сдвига | Выходное значение массива сдвига | ||||

|---|---|---|---|---|---|

| HI | LO | ||||

| +16…+127 | +32…+127 | 00000000 | 00000000 | 00000000 | 00000000 |

| +15 | +31 | R0000000 | 00000000 | 00000000 | 00000000 |

| +14 | +30 | PR000000 | 00000000 | 00000000 | 00000000 |

| +13 | +29 | NPR00000 | 00000000 | 00000000 | 00000000 |

| +12 | +28 | MNPR0000 | 00000000 | 00000000 | 00000000 |

| +11 | +27 | LMNPR000 | 00000000 | 00000000 | 00000000 |

| +10 | +26 | KLMNPR00 | 00000000 | 00000000 | 00000000 |

| +9 | +25 | JKLMNPR0 | 00000000 | 00000000 | 00000000 |

| +8 | +24 | IJKLMNPR | 00000000 | 00000000 | 00000000 |

| +7 | +23 | HIJKLMNP | R0000000 | 00000000 | 00000000 |

| +6 | +22 | GHIJKLMN | PR000000 | 00000000 | 00000000 |

| +5 | +21 | FGHIJKLM | NPR00000 | 00000000 | 00000000 |

| +4 | +20 | EFGHIJKL | MNPR0000 | 00000000 | 00000000 |

| +3 | +19 | DEFGHIJK | LMNPR000 | 00000000 | 00000000 |

| +2 | +18 | CDEFGHIJ | KLMNPR00 | 00000000 | 00000000 |

| +1 | +17 | BCDEFGHI | GKLMNPR0 | 00000000 | 00000000 |

| 0 | +16 | ABCDEFGH | IJKLMNPR | 00000000 | 00000000 |

| -1 | +15 | XABCDEFG | HIJKLMNP | R0000000 | 00000000 |

| -2 | +14 | XXABCDEF | GHIJKLMN | PR000000 | 00000000 |

| -3 | +13 | XXXABCDE | FGHIJKLM | NPR00000 | 00000000 |

| -4 | +12 | XXXXABCD | EFGHIJKL | MNPR0000 | 00000000 |

| -5 | +11 | ХХХХХАВС | DEFGHIJK | LMNPR000 | 00000000 |

| -6 | +10 | ХХХХХХАВ | CDEFGHIJ | KLMNPR00 | 00000000 |

| -7 | +9 | XXXXXXXA | BCDEFGHI | JKLMNPR0 | 00000000 |

| -8 | +8 | XXXXXXXX | ABCDEFGH | IJKLMNPR | 00000000 |

| -9 | +7 | XXXXXXXX | XABCDEFG | HIJKLMNP | R0000000 |

| -10 | +6 | XXXXXXXX | XXABCDEF | GHIJKLMN | PR000000 |

| -11 | +5 | XXXXXXXX | XXXABCDE | FGHIJKLM | NPR00000 |

| -12 | +4 | XXXXXXXX | XXXXABCD | EFGHIJKL | MNPR0000 |

| -13 | +3 | XXXXXXXX | ХХХХХАВС | DEFGHIJK | LMNPR000 |

| -14 | +2 | XXXXXXXX | ХХХХХХАВ | CDEFGHIJ | KLMNPR00 |

| -15 | +1 | XXXXXXXX | ХХХХХХХА | BCDEFGHI | JKLMNPR0 |

| -16 | 0 | XXXXXXXX | ХХХХХХХХ | ABCDEFGH | IJKLMNPR |

| -17 | -1 | XXXXXXXX | ХХХХХХХХ | XABCDEFG | HIJKLMNP |

| -18 | -2 | XXXXXXXX | ХХХХХХХХ | XXABCDEF | GHIJKLMN |

| -19 | -3 | XXXXXXXX | ХХХХХХХХ | XXXABCDE | FGHIJKLM |

| -20 | -4 | XXXXXXXX | ХХХХХХХХ | XXXXABCD | EFGHIJKL |

| -21 | -5 | XXXXXXXX | ХХХХХХХХ | ХХХХХАВС | DEFGHIJK |

| -22 | -6 | XXXXXXXX | ХХХХХХХХ | ХХХХХХАВ | CDEFGHIJ |

| -23 | -7 | XXXXXXXX | ХХХХХХХХ | XXXXXXXA | BCDEFGHI |

| -24 | -8 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | ABCDEFGH |

| -25 | -9 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | XABCDEFG |

| -26 | -10 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | XXABCDEF |

| -27 | -11 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | XXXABCDE |

| -28 | -12 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | XXXXABCD |

| -29 | -13 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | ХХХХХАВС |

| -30 | -14 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | ХХХХХХАВ |

| -31 | -15 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | ХХХХХХХА |

| -32…-128 | -16…-128 | XXXXXXXX | ХХХХХХХХ | XXXXXXXX | ХХХХХХХХ |

Массив сдвига и связанная с ним логика OR/PASS находятся в окружении набора регистров. Входной регистр SI (Shifter Input) содержит данные для массива сдвига и детектора порядка. Разрядность регистра SI составляет 16 бит.

Этот регистр записывается с DMD-шины. В качестве входных регистров для массива сдвига и детектора порядка могут служить регистры AR, SR или MR, подключенные через R-шину. Выходной 32-разрядный регистр SR (Shifter Result) разделен на два 16- разрядных регистра SR0 и SR1. Загрузка данных в эти регистры может производиться с DMD-шины, а результат выводится на R-шину или DMD-шину. Регистр SR подключен к блоку OR/PASS логики для проведения сдвигов двойной точности.

Регистр SE (Shifter Exponent) состоит из 8 разрядов и содержит порядок во время нормализации и денормализации данных. Он доступен через 8 младших разрядов DMD-шины. Его формат 8.0 в дополнительном коде.

Регистр SB (Shifter Block) используется в блочных операциях для чисел с плавающей точкой. Его значение определяет сдвиг для нормализации чисел в блоке данных, т.е. значение, на которое должен произойти сдвиг для нормализации самого большого числа в блоке данных. Разрядность регистра SB составляет 5 бит. Он доступен через 5 младших разрядов DMD-шины. Его формат 5.0 в дополнительном коде.

При чтении регистров SE и SB на DMD-шину числа автоматически дополняются знаковыми битами до 16-разрядного значения. Любой из регистров SI, SE, SR может быть прочитан или записан в одном и том же цикле.

Shifter также имеет банк теневых регистров SI, SE, SR и SB. Выбор банка регистров производится установкой нулевого бита регистра режима MSTAT процессора.

Устройство сдвига заполняет все биты 32-разрядного результата правее сдвига нулями, а левее сдвига битом расширения. Бит расширения может принимать значение знакового бита, бита флага АС из регистра ASTAT или нулевое значение, в зависимости от выполняемой инструкции.

Логика OR/PASS позволяет правильно комбинировать сдвинутые секции числа с двойной точностью. При выборе инструкции PASS результат массива сдвигов загружается в регистр SR без изменения. При выборе инструкции OR результат массива сдвигов подвергается операции «ЛОГИЧЕСКОЕ ИЛИ» с предыдущим значением регистра SR и после этого вновь помещается в SR.

Детектор порядка вычисляет степень из входного операнда устройства сдвига. Входное значение для него интерпретируется в зависимости от одного из трех режимов, в котором он работает.

В режиме HI входной операнд воспринимается как число с одинарной точностью или как старшая половина числа с двойной точностью. Детектор степени определяет количество знаковых разрядов и формирует код, который будет служить для сдвига данных влево так, чтобы оставить в данных только один знаковый разряд.

В режиме HIX входной операнд воспринимается как результат сложения или вычитания, выполненного в ALU, когда могло произойти переполнение. Поэтому детектор степени берет в учет значение флага AV регистра ASTAT. Если он установлен, формируется дополнительный бит для нормирования данных. Если флаг сброшен, отличий между режимами HI и HIX нет. В режимах HI и HIX детектор степени формирует бит знака SS (Shifter Sing), который помещается в регистр ASTAT устройства ALU. Он соответствует старшему разряду входного операнда, за исключением тех случаев, когда установлен флаг AV в режиме HIX. В этом случае формируется отрицание старшего разряда входного операнда, для сохранения знака переполненного значения.

В режиме LO входной операнд интерпретируется как младшая половина числа с двойной точностью. В этом режиме детектор степени интерпретирует бит SS как знак числа. Регистр SE загружается результатом детектора порядка только в том случае, если регистр SE равен минус 15. Это происходит в тех случаях, когда старшая часть числа содержит лишь знаковые разряды. При этом выходное значение детектора порядка сдвигается на 16 разрядов влево, для того чтобы определить, что операнд является младшей половиной 32-разрядного числа.

Для наглядности, в табл. 16.3–16.5 показаны все три режима работы детектора порядка. В таблицах приняты следующие условные обозначения: S — знаковый бит, N — знаковый бит, D — незначащий бит.

Таблица 16.3 Детектор порядка в режиме работы HI

| Старший байт | Младший байт | Степень |

|---|---|---|

| SNDDDDDD | DDDDDDDD | 0 |

| SSNDDDDD | DDDDDDDD | -1 |

| SSSNDDDD | DDDDDDDD | -2 |

| SSSSNDDD | DDDDDDDD | -3 |

| SSSSSNDD | DDDDDDDD | -4 |

| SSSSSSND | DDDDDDDD | -5 |

| SSSSSSSN | DDDDDDDD | -6 |

| SSSSSSSS | NDDDDDDD | -7 |

| SSSSSSSS | SNDDDDDD | -8 |

| SSSSSSSS | SSNDDDDD | -9 |

| SSSSSSSS | SSSNDDDD | -10 |

| SSSSSSSS | SSSSNDDD | -11 |

| SSSSSSSS | SSSSSNDD | -12 |

| SSSSSSSS | SSSSSSND | -13 |

| SSSSSSSS | SSSSSSSN | -14 |

| SSSSSSSS | SSSSSSSS | -15 |

Таблица 16.4 Детектор порядка в режиме работы HIX

| Флаг AV | Старший байт | Младший байт | Степень |

|---|---|---|---|

| 1 | DDDDDDDD | DDDDDDDD | +1 |

| 0 | SNDDDDDD | DDDDDDDD | 0 |

| 0 | SSNDDDDD | DDDDDDDD | -1 |

| 0 | SSSNDDDD | DDDDDDDD | -2 |

| 0 | SSSSNDDD | DDDDDDDD | -3 |

| 0 | SSSSSNDD | DDDDDDDD | -4 |

| 0 | SSSSSSND | DDDDDDDD | -5 |

| 0 | SSSSSSSN | DDDDDDDD | -6 |

| 0 | SSSSSSSS | NDDDDDDD | -7 |

| 0 | SSSSSSSS | SNDDDDDD | -8 |

| 0 | SSSSSSSS | SSNDDDDD | -9 |

| 0 | SSSSSSSS | SSSNDDDD | -10 |

| 0 | SSSSSSSS | SSSSNDDD | -11 |

| 0 | SSSSSSSS | SSSSSNDD | -12 |

| 0 | SSSSSSSS | SSSSSSND | -13 |

| 0 | SSSSSSSS | SSSSSSSN | -14 |

| 0 | SSSSSSSS | SSSSSSSS | -15 |

Таблица 16.5 Детектор порядка в режиме работы LO

| Флаг SS | Старший байт | Младший байт | Степень |

|---|---|---|---|

| S | DDDDDDDD | DDDDDDDD | -15 |

| S | SNDDDDDD | DDDDDDDD | -16 |

| S | SSNDDDDD | DDDDDDDD | -17 |

| S | SSSNDDDD | DDDDDDDD | -18 |

| S | SSSSNDDD | DDDDDDDD | -19 |

| S | SSSSSNDD | DDDDDDDD | -20 |

| S | SSSSSSND | DDDDDDDD | -21 |

| S | SSSSSSSN | DDDDDDDD | -22 |

| S | SSSSSSSS | NDDDDDDD | -23 |

| S | SSSSSSSS | SNDDDDDD | -24 |

| S | SSSSSSSS | SSNDDDDD | -25 |

| S | SSSSSSSS | SSSNDDDD | -26 |

| S | SSSSSSSS | SSSSNDDD | -27 |

| S | SSSSSSSS | SSSSSNDD | -28 |

| S | SSSSSSSS | SSSSSSND | -29 |

| S | SSSSSSSS | SSSSSSSN | -30 |

| S | SSSSSSSS | SSSSSSSS | -31 |

Источниками входных данных в устройстве сдвига могут служить регистры SI, AR, MR0, MR1, MR2, SR0 и SR1. Результат работы устройства сдвига всегда помещается в регистр SR (SR0, SR1).

Как было сказано выше, устройство сдвига выполняет следующие функции:

• Арифметический сдвиг (ASHIFT)

• Логический сдвиг (LSHIFT)

• Нормализация числа (NORM)

• Определение экспоненты (ЕХР)

• Блочное изменение экспоненты (EXPADJ)

Данные команды устройства сдвига применяются при выполнении арифметических операций над числами. С их помощью производится определение порядка блока, немедленные сдвиги, нормализация и денормализация чисел.

Ниже приводится полный список команд устройства сдвига Shifter в соответствии с принятыми ранее условными сокращениями. Назначение команд приводится в тексте описания этих команд и комментариях для некоторых из команд.

Команды арифметического сдвига:

[IF cond] SR = |SR OR| ASHIFT xop |(HI)|; |(LO)|Команды логического сдвига:

[IF cond] SR = |SR OR| LSHIFT xop |(HI)|; |(LO)|Команды нормализации:

[IF cond] SR = |SR OR| NORM xop |(HI)|; |(LO)|Команды выделения порядка:

[IF cond] SR = EXP xop |(HI) |; |(LO) | |(HIX)|Команды выравнивания блочного порядка:

[IF cond] SR = EXPADJ xop;Команды арифметического непосредственного сдвига:

[IF cond] SR = |SR OR| ASHIFT xop BY |(HI)|; |(LO)|Команды логического непосредственного сдвига:

[IF cond] SR = |SR OR| LSHIFT xop BY |(HI)|; |(LO)|В записях некоторых команд присутствуют символы, которые имеют следующее назначение:

HI — сдвиг выполняется относительно старших 16 разрядов (SR1);

LO — сдвиг выполняется относительно младших 16 разрядов (SR0);

HIX — расширенный режим HI (при выделении порядка учитывается бит переполнения AV).

Например, команда:

SE=EXP AR (HIX);означает, что в регистр SE будет занесен результат выделения порядка из регистра AR в расширенном режиме, т.е. с учетом бита переполнения AV.

Команда:

SR=NORM AR (HI); {Нормализация}означает, что в регистр SR будет занесен результат нормализации регистра AR, причем сдвиг при нормализации будет выполняться относительно старших 16 разрядов.

Для всех команд устройства сдвига разрешено использовать следующие операнды xop: SI, SR0, SR1, AR, MR0, MR1, MR2, а в качестве ЕХР может быть любое целое число от -128 до 127.

Коды условия IF соответствуют кодам, приведенным ранее в табличном виде.

Ниже приведен пример программы для вычисления разницы двух чисел в формате с плавающей точкой, с применением устройства сдвига.

.MODULE float_point_sub;{ Программный модуль вычисления z = x - y в формате с плавающей точкой Входные операнды: AX0 = показатель x, АХ1 = мантисса x, AY0 = показатель y, AY1 = мантисса y. Выходные данные: AR = показатель z, SR1 = мантисса z Изменяются регистры: AX0,AY1,AY0,AF,AR,SI,SE,SR Время вычисления = 11 циклов}.ENTRY fps;fps : AF=AX0-AY0; {Показатель x > показателя y?}IF GT JUMP shifty; {Если да - переход на сдвиг y}SI=AX1, AR=PASS AF; {Иначе - сдвиг x}SE=AR;SR=ASHIFT SI (HI);AR=SR1-AY1; {Вычисление мантиссы}JUMP subt;shifty: SI=AY1, AR=-AF; SE=AR;SR=ASHIFT SI (HI);AY1=SR1;AY0=AX0, AR=AX1-AY1; {Вычисление мантиссы}subt: SE=EXP AR (HIX);AX0=SE, SR=NORM AR (HI); {Нормализация}AR=AX0+AY0; {Вычисление показателя}RTS;.ENDMOD;Данная программа содержит многофункциональные команды, что позволило сократить время ее работы. Программа выполняется всего за 11 машинных циклов процессора.

Глава 17. Устройство обмена между шинами

В этой главе говорится об устройстве обмена между шинами памяти программ PMD и памяти данных DMD.

В этой главе говорится об устройстве обмена между шинами памяти программ PMD и памяти данных DMD.

В операциях обмена данными и при загрузке данных вычислительными устройствами процессора, часто используется устройство обмена между шиной памяти программ PMD и шиной памяти данных DMD. Это устройство позволяет передавать данные между упомянутыми выше шинами в обоих направлениях. Рассмотрим работу данного устройства. Его структурная схема приведена на рис. 17.1.

Рис. 17.1. Устройство обмена между шинами памяти программ PMD и памяти данных DMD

Как видно из рисунка, устройство состоит из нескольких буферов, мультиплексора и регистра PX. Регистр PX используется для временного хранения 8 разрядов данных. Он необходим для обеспечения корректной передачи данных между 16-разрядной шиной DMD и 24-разрядной шиной PMD. При этом старшие 16 разрядов 24-разрядной шины PMD передаются на 16 разрядов шины DMD непосредственно, а 8 младших разрядов записываются в регистр PX, а затем передаются на младшие 8 разрядов шины DMD.

Из структурной схемы устройства видно, что данные между шинами передаются двумя путями. Первый путь позволяет осуществлять прямую пересылку старших 16 разрядов данных между шинами через буферные регистры. Второй путь служит для пересылки младших 8 разрядов данных между шинами.

Рассмотрим механизм обмена данными с использованием регистра PX.

Когда данные считываются из памяти программ в любой регистр, происходит автоматическая загрузка регистра PX младшими 8 разрядами 24-разрядного слова. Например:

AX0 = PM(I7,M7);При выполнении этой команды старшие 16 разрядов 24-разрядного слова памяти программы загружаются в регистр AX0, а младшие 8 разрядов автоматически загружаются в регистр PX.

При записи данных в память программ содержимое регистра PX автоматически считывается в младшие 8 разрядов памяти программ. Например:

PM(I7,M7) = AX0;Здесь данные регистра AX0 записываются в старшие 16 разрядов 24-разрядного слова памяти программы, а 8 разрядов, хранящиеся в регистре PX от предыдущей команды, автоматически записываются в младшие 8 разрядов этого же слова. Таким образом, достигается автоматическая пересылка данных между 16- и 24-разрядными шинами.

Кроме того, существуют команды прямого доступа к регистру PX с шины памяти данных. При этом используются только младшие 8 разрядов шины данных, а старшие 8 разрядов данных отбрасываются или заполняются нулями. Например:

PX = AX0;Эта команда передает в регистр PX 8 младших разрядов из регистра AX0 через шину данных. Восемь старших разрядов 16-разрядного слова при этом отбрасываются.

Следующая команда передает содержимое регистра PX в 8 младших разрядов регистра AX0. При этом старшие 8 разрядов регистра AX0 заполняются нулями.

AX0 = PX;Каждый раз, когда содержимое какого-либо регистра записывается в память программ, из этого регистра передаются 16 старших разрядов, а содержимое регистра PX автоматически добавляется в качестве младших 8 разрядов данных. Если эти 8 младших разрядов регистра PX должны иметь определенное значение, они должны быть предварительно загружены в регистр PX соответствующей командой.

Ниже приведен модуль программы, предназначенной для пересылки 24-разрядных данных из одной области памяти программ в другую при помощи 16-разрядного регистра.

.MODULE copy_pdm;{ Входные данные: I4= адрес источника данных L4 = длина буфера данных I5= адрес приемника данных Выходные данные: Перемещенные данные Изменяемые регистры: AR, M4}.ENTRY COPY_PMDAT;COPY_PMDAT: M4=1; CNTR = L4; DO COPY_MEM UNTIL СЕ; AR=PM(I4, M4); PM(I5, M4)=AR; COPY_MEM: RTS;.ENDMOD;Обратите внимание, что в этой программе регистр PX не используется явным образом в командах, тем не менее, пересылка 24-разрядных данных через 16-разрядный регистр AR осуществляется корректно, благодаря автоматическому режиму работы устройства обмена данными с применением регистра PX.

Глава 18. Программный автомат

В этой главе говорится о программном автомате сигнального процессора и выполняемых с его помощью командах.

В этой главе говорится о программном автомате сигнального процессора и выполняемых с его помощью командах.

Программный автомат управляет последовательностью выполнения программы. Он содержит контроллер прерываний и логическое устройство состояний. Программный автомат позволяет осуществлять последовательное выполнение команд, условные и безусловные переходы в программе, обработку прерываний и подпрограмм. Структурная схема этого устройства приведена на рис. 18.1.

Рис. 18.1. Программный автомат сигнального процессора

Основным блоком программного автомата является программный счетчик (PC-program counter). Он представляет собой 14- разрядный регистр, в котором постоянно содержится адрес текущей выполняемой команды. Это значение инкрементируется (увеличивается на 1) каждый раз при выполнении очередной последовательной команды.

Стек программного счетчика служит для временного хранения адреса очередной команды при переходе на обработку подпрограммы, цикловой операции или прерывания. Он позволяет хранить до шестнадцати 14-разрядных слов. Таким образом, уровень вложенности подпрограмм не должен превышать 16.

Контроллер прерываний формирует адрес подпрограммы обработчика прерывания. Он использует данные регистров статуса и влияет на выбор источника следующего адреса.

Блоки счетчика циклов, стека счетчика, компаратора циклов и стека циклов позволяют организовать цикловые операции в программе, не привлекая для этого другие регистры процессора.

Логика выбора формирует сигнал для выбора источника следующего адреса команды.

Ниже приводится полный список команд, выполняемых программным автоматом в соответствии с принятыми ранее условными сокращениями. Назначение команд приводится в тексте описания этих команд и комментариях для некоторых из команд.

Выполнять цикл до определенного условия:

DO [UNTIL term]; Условный (безусловный) переход:

[IF cond] JUMP |(I4) |; |(I5) | |(I6) | |(I7) | || Вызов подпрограммы:

[IF cond] CALL |(I4) |; |(I5) | |(I6) | |(I7) | || Переход (вызов подпрограммы) по состоянию вывода флага Flag In:

[IF] |FLAG_IN | |JUMP| ; |IF NOT FLAG_IN | |CALL|Изменение состояния вывода флагов:

[IF cond] |SET | |FLAG_OUT | [,...]; {установка флага} |RESET | |FL0 | {сброс флага} |TOGGLE | |FL1 | {инверсия флага} |FL2 |Возврат из подпрограммы:

[IF cond] RTS;Возврат из подпрограммы прерывания:

[IF cond] RTI;Ожидание прерываний:

IDLE;Команда переводит процессор в режим пониженного потребления на некоторое неопределенное время. Для того, чтобы перевести процессор в этот режим на продолжительное время, необходимо после этой команды вставить команду перехода на IDLE, зациклив тем самым программу. Выход из этого режима произойдет по любому прерыванию процессора.

Допустимые значения

CNTR=100; {Заполнить счетчик циклов}DO Met1 UNTIL CE; {Выполнить цикл до метки Met1, пока счетчик циклов не пуст}AX0 = DM(I0,M0); {Переслать данные через регистр AX0}Met1: DM(I1 ,M1 )=AX0; {в новую область памяти}JUMP(I4); {Осуществить переход по адресу в индексном регистре I4}CALL (I6); {Вызвать подпрограмму по адресу в индексном регистре I6}SET FLAG_OUT; {Установить в 1 вывод FLAG_OUT}RESET FL2 {Сбросить флаг FL2}TOGGLE FL0 {Инвертировать флаг FL0}Met2: IDLE; {Режим ожидания прерывания}JUMP Met2:Таблица 18.1 Допустимые значения

| Значение |

Пояснение |

|---|---|

| CE | Счетчик циклов пуст |

| EQ | Равно нулю |

| NE | Не равно нулю |

| LT | Меньше нуля |

| GE | Больше или равно нулю |

| LE | Меньше или равно нулю |

| GT | Больше нуля |

| АС | Перенос АЛУ |

| NOT AC | Нет переноса АЛУ |

| AV | Переполнение АЛУ |

| NOT AV | Нет переполнения АЛУ |

| MV | Переполнение умножителя |

| NOT MV | Нет переполнения умножителя |

| NEG | Входной операнд «xop» отрицателен |

| POS | Входной операнд «xop» положителен |

| FOREVER | Бесконечный цикл |

Таблица 18.2 Допустимые значения

| Значение |

Пояснение |

|---|---|

| EQ | Равно нулю |

| NE | He равно нулю |

| LT | Меньше нуля |

| GE | Больше или равно нулю |

| LE | Меньше или равно нулю |

| GT | Больше нуля |

| AC | Перенос АЛУ |

| NOT AC | Нет переноса АЛУ |

| AV | Переполнение АЛУ |

| NOT AV | Нет переполнения АЛУ |

| MV | Переполнение умножителя |

| NOT MV | Нет переполнения умножителя |

| NEG | Входной операнд «xop» отрицателен |

| POS | Входной операнд «xop» положителен |

| NOT CE | Счетчик циклов не пуст |

| FLAG_IN* | Вывод FI=1 |

| NOT FLAG_IN* | Вывод FI=0 |

*Только для команд JUMP, CALL

Глава 19. Генераторы адресов

В этой главе говорится об устройствах генераторов адресов сигнального процессора и выполняемых с его помощью командах.

В этой главе говорится об устройствах генераторов адресов сигнального процессора и выполняемых с его помощью командах.

Ранее мы уже рассматривали назначение генераторов адресов (DAG). На этот раз рассмотрим их структуру и команды, которые они позволяют выполнять.

Сигнальный процессор имеет в своем составе два независимых генератора адреса данных, обеспечивающих одновременный доступ к памяти данных и памяти программ. Генераторы адреса осуществляют косвенную адресацию данных. Оба генератора могут выполнять автоматическую модификацию адреса данных. С помощью циклических буферов, они могут выполнять модификацию адреса по модулю. Отличие генераторов адреса друг от друга состоит в следующем. Первый генератор адреса (DAG1) генерирует только адреса памяти данных, но обеспечивает при этом изменение порядка разрядов в адресе на обратный (реверс разрядов). Второй генератор адреса (DAG2) генерирует как адреса памяти данных, так и адреса памяти программы, но не способен поддерживать реверсную адресацию.

Структурная схема генератора адреса приведена на рис. 19.1. Отличия структуры DAG1 от DAG2 показаны на самой схеме.

Рис. 19.1. Структурная схема генератора адреса

Каждый генератор имеет в своем составе три регистровых блока: блок регистров модификации (M), блок индексных регистров (I) и блок регистров длины (L). Каждый из регистровых блоков состоит из четырех регистров разрядностью 14 бит. Чтение и запись данных в эти регистры осуществляется через шину данных DMD. Индексные регистры I содержат действительные адреса, используемые для доступа к памяти. При косвенной адресации данных адрес, находящийся в выбранном индексном регистре, становится адресом памяти. Разряды адреса на выходе DAG1 могут быть переставлены в обратном порядке за счет установки соответствующего бита режима в регистре состояний режима MSTAT или при помощи команды ENA BIT_REV. Реверс адреса (адресация с перестановкой разрядов в обратном порядке) необходим для выполнения операций БПФ (быстрого преобразования Фурье) для цифровых значений сигнала. Данную операцию часто называют скремблированием (от английского слова scramble — смешивать). Сброс бита режима реверса адреса в регистре состояний режима MSTAT производится командой DIS BIT_REV. Для наглядности сказанного в табл. 19.1 приведен нормальный и реверсивный порядок адресов для 2-, 3- и 4-разрядных адресов. Из таблицы видно, каким образом при этом перемешиваются значения адреса.

Таблица 19.1 Нормальный и реверсивный порядок адресов для 2-, 3- и 4-разрядных адресов

| Значение адреса | Нормальный порядок | Реверсивный порядок | Значение адреса |

|---|---|---|---|

| 2-разрядный адрес | |||

| 0 | 00 | 00 | 0 |

| 1 | 01 | 10 | 2 |

| 2 | 10 | 01 | 1 |

| 3 | 11 | 11 | 3 |

| 3-разрядный адрес | |||

| 0 | 000 | 000 | 0 |

| 1 | 001 | 100 | 4 |

| 2 | 010 | 010 | 2 |

| 3 | 011 | 110 | 6 |

| 4 | 100 | 001 | 1 |

| 5 | 101 | 101 | 5 |

| 6 | 110 | 011 | 3 |

| 7 | 111 | 111 | 7 |

| 4-разрядный адрес | |||

| 0 | 0000 | 0000 | 0 |

| 1 | 0001 | 1000 | 8 |

| 2 | 0010 | 0100 | 4 |

| 3 | 0011 | 1100 | 12 |

| 4 | 0100 | 0010 | 2 |

| 5 | 0101 | 1010 | 10 |

| 6 | 0110 | 0110 | 6 |

| 7 | 0111 | 1110 | 14 |

| 8 | 1000 | 0001 | 1 |

| 9 | 1001 | 1001 | 9 |

| 10 | 1010 | 0101 | 5 |

| 11 | 1011 | 1101 | 13 |

| 12 | 1100 | 0011 | 3 |

| 13 | 1101 | 1011 | 11 |

| 14 | 1110 | 0111 | 7 |

| 15 | 1111 | 1111 | 15 |

Генераторы адреса используют пост-модификацию. Т.е. после доступа к данным при использовании косвенной адресации содержимое заданного регистра модификации M прибавляется к содержимому индексного регистра I для формирования нового значения регистра I. Выбор регистров M и I в пределах одного DAG произволен. Т.е. любой из индексных регистров I0–I3 DAG1 может быть модифицирован содержимым любого из регистров модификации M0–M3. Для DAG2 аналогично используются регистры I4–I7 и M4–M7. Значения модификации, содержащиеся в регистрах модификации M, являются знаковыми числами, поэтому следующий вычисленный адрес может быть больше или меньше предыдущего.

Генераторы адреса поддерживают адресацию линейных и циклических буферов данных. Содержимое регистра длины L определяет режим адресации для соответствующего индексного регистра I. При адресации циклических буферов регистр L инициализируется длиной буфера. При адресации линейных буферов регистр L инициализируется нулем. Для каждого регистра I соответствующий регистр L несет информацию о длине буфера. Если сумма значений регистра модификации M и индексного регистра I превышает значение длины циклического буфера, модифицированное значение регистра I вычисляется логическим устройством адресации по модулю с использованием значения регистра длины L.

Поскольку регистры I и L содержат беззнаковые числа, два старших разряда шины данных заполняются при чтении этих регистров нулями. Регистры модификации M хранят числа со знаком, поэтому старшие два разряда шины данных дополняются знаковым расширением при их чтении.

Логическое устройство инвертирования разрядов адреса предназначено для вычислений БПФ, когда разряды двоичных значений данных вводятся или генерируются в обратном порядке. Постановка разрядов в обратном порядке возможна только для адресов, генерируемых DAG1. Точкой поворота является средняя точка 14-разрядного адреса, между разрядами 6 и 7, как показано ниже:

Нормальный порядок разрядов:

13 12 11 10 09 08 07 06 05 04 03 02 01 00.

Реверсный порядок разрядов:

00 01 02 03 04 05 06 07 08 09 10 11 12 13.

Реверсная адресация разрешается при установке соответствующего бита в регистре состояния режима MSTAT. При разрешении данного режима работы DAG1 разряды всех адресов, сгенерированных с использованием индексных регистров I0–I3, ставятся в обратном порядке на выходе. При этом значения адресов в индексных регистрах хранятся в нормальном порядке, а преобразование адреса происходит только при выводе на шину адреса. Этот режим сохраняется до сброса соответствующего бита состояния MSTAT.

В DAG1 можно также инвертировать значения адресов с разрядностью менее 14 бит. Для этого необходимо определить первый адрес и записать при инициализации в регистр модификации M значение, вычисляемое для модификации инвертированного выходного значения регистра I в нужном интервале. Это значение равно 214-N, где N - число разрядов, которое необходимо поставить в обратном порядке.

Поскольку генераторы адресов используются для формирования адресов данных, эти устройства используются в командах пересылки данных. Ниже приводится полный список команд пересылки данных в соответствии с принятыми ранее условными обозначениями. Назначение команд приводится в тексте описания этих команд.

Чтение из памяти данных (косвенная адресация):

dreg = DM(|I0|,|M0|); |I1|,|M1| |I2|,|M2| |I3|,|M3| |I4|,|M4| |I5|,|M5| |I6|,|M6| |I7|,|M7|Чтение из памяти программ (косвенная адресация):

dreg = PM(|I4|,|M4|); |I5|,|M5| |I6|,|M6| |I7|,|M7|Запись в память данных (косвенная адресация):

DM(|I0|,|M0|) = dreg; |I1|,|M1| |I2|,|M2| |I3|,|M3| |I4|,|M4| |I5|,|M5| |I6|,|M6| |I7|,|M7|Запись в память программ (косвенная адресация):

PM(|I4|,|M4|) = dreg; |I5|,|M5| |I6|,|M6| |I7|,|M7|Запись в память данных (прямая адресация):

DM() = reg; Запись содержимого регистров оверлеев в память данных:

DM() = DMOVLAY; Запись в область ввода/вывода (прямая адресация):

IO() = dreg; Пересылка регистр-регистр:

reg = reg;Непосредственная загрузка регистра:

reg = ;dreg = ;Чтение регистра оверлеев:

dreg = DMOVLAY;Запись в регистр оверлеев:

DMOVLAY = dreg;Чтение из памяти данных (прямая адресация):

reg = DM (); Чтение из памяти ввода/вывода (прямая адресация):

dreg = IO(); Символьная запись

Вместо записи dreg могут быть использованы регистры: AX0, АХ1, AY0, AY1, AR, MX0, МХ1, MY0, MY1, MR0, MR1, MR2, SI, SE, SR0, SR1.

Вместо записи reg могут быть использованы все регистры dreg и регистры: I0–I7, M0–M7, L0–L7, TX0, ТХ1, RX0, RX1, SB, PX, ASTAT, MSTAT, SSTAT(только чтение), IMASK, ICNTL, IFC (только запись), CNTR, OWRCNTR (только запись).

Примеры команд пересылки данных:

AX0=АХ1; {Переслать содержимое регистра AX1 в AX0}AY0=0xA37F; {Загрузить в регистр 16-разрядное число 0xA37F}AY0=DM(1247); {Прочесть данные из ячейки памяти с адресом 1247 в регистр AY0}PM(I7, M7) = AX0; {Записать в память программ значение регистра AX0, используя индексные регистры I7 и M7}Ниже приведен пример подпрограммы реверсирования разрядов адреса. Данная программа служит для размещения данных по адресам, в которых изменен нормальный порядок разрядов на обратный порядок.

.MODULE scram;{ Вход: Буфер данных input Выход: Буфер данных output Используемые регистры: I0, I4, M0, М4, AY1}.CONST N=1025, mv=H#0010; {Инициализация констант mv=16384/N}.EXTERNAL input, output;.ENTRY scramble;scramble: I4=^input; {I4 присвоить адрес начала буфера входных данных}I0=^output; {I0 присвоить адрес начала буфера выходных данных}M4=1;M0=mv; {M0=модификатор для реверса}L4=0; {Линейные буферы}L0=0;ENA BIT_REV; {Разрешение инвертирования разрядов}CNTR=N;DO Met UNTIL СЕ; {Организация цикла}AY1 =DM(I4,M4); {Чтение последовательно организованных данных}Met: DM(I0,M0)=AY1; {Запись данных в ячейки в обратном порядке}DIS BIT_REV; {Запрещение инвертирования разрядов}RTS; {Возврат в вызывающую программу}.ENDMOD;

Глава 20. Таймер

В этой главе говорится об устройстве таймера сигнального процессора и его назначении.

В этой главе говорится об устройстве таймера сигнального процессора и его назначении.

Кроме рассмотренных нами вычислительных устройств, сигнальный процессор содержит в своем составе программируемый таймер, обеспечивающий автоматический отсчет времени, и два программируемых последовательных порта для связи с внешней периферией. Рассмотрим поочередно эти устройства.

Программируемый таймер сигнального процессора позволяет циклически генерировать прерывания через определенные промежутки времени, кратные циклам процессора. Структурная схема таймера представлена на рис. 20.1.

Рис. 20.1. Структурная схема таймера

Как видно из рисунка, таймер включает в себя 16-разрядный регистр периода TPERIOD, 8-разрядный регистр масштабирования TSCALE, 16-разрядный регистр-счетчик TCOUNT и логику управления. Все три регистра отображены на область памяти данных процессора в соответствии с табл. 20.1.

Таблица 20.1 Формат регистров таймера, отображенных на память данных процессора

| Разряды регистров | Адрес | |||||||

|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0x3FFB |

| Разряды регистров | Адрес | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| TSCALE | 0x3FFB |

Разрешение работы таймера производится установкой в единицу 5-го разряда регистра состояния процессора MSTAT. Когда работа таймера разрешена, регистр-счетчик TCOUNT декрементируется сигналами от логики масштабирования. При достижении счетчиком нуля, формируется прерывание таймера для процессора. После чего в регистр-счетчик TCOUNT автоматически загружается значение регистра периода TPERIOD и работа таймера продолжается.

Регистр масштабирования TSCALE содержит коэффициент деления тактовой частоты процессора и позволяет изменять время между прерываниями таймера.

Значения регистров TPERIOD и TSCALE могут загружаться с шины DMD. Таким образом, с помощью таймера можно генерировать прерывания каждые (TPERIOD+1)*(TSCALE+1) циклов, т.е. от 1 до FFFFFF16=1677721510 циклов. При тактовой частоте процессора 40МГц таймер может формировать прерывания с периодом от 20 нс до 0,3 с.

При необходимости прерывания таймера можно маскировать, сбрасывать или принудительно устанавливать программным образом.

Ниже приведен пример команд инициализации таймера:

{Регистр таймера TPERIOD=0x3FFD (Регистр периода)}AX0=0X7FFF; DM(TPERIOD)=AX0;{Регистр таймера TCOUNT=0x3FFC (Регистр счетчика)}AX0=0X7FFF; DM(TCOUNT)=AX0;{Регистр таймера TSCALE=0x3FFB (Регистр масштабирования)}AX0=255; {ОТ 0 ДО 255} DM(TSCALE)=AX0;Строка обработки прерывания в программе может иметь следующий вид:

jump V_TIMER; nop; nop; nop; {Вектор прерывания таймера}Следующий пример обработчика прерывания таймера позволяет автоматически наращивать значения ячейки памяти 0x3000 и выводить эти значения в порт ввода-вывода по адресу 2000.

{===== Обработчик прерывания таймера =====}V_TIMER:ENA SEC_REG;AX0=DM(0X3000);AR=AX0 + 1;DM(0X3000)=AR;IO(2000)=AR;RTI;Подобным образом можно организовывать автоматическую регенерацию динамической памяти, подключаемой к сигнальному процессору. Учитывая, что объем такого типа памяти составляет десятки миллионов байт в одной микросхеме, можно догадаться о мощности устройств, создаваемых с ее применением. В то же время регенерация динамической памяти очень легко решается при подключении ее к сигнальному процессору.

Глава 21. Синхронные последовательные порты

В этой главе говорится о двух синхронных последовательных портах, входящих в состав сигнального процессора, об их устройстве, назначении и использовании.

В этой главе говорится о двух синхронных последовательных портах, входящих в состав сигнального процессора, об их устройстве, назначении и использовании.

Кроме рассмотренных нами вычислительных и других устройств, сигнальный процессор имеет встроенные коммуникационные средства в виде двух синхронных последовательных портов, называемых SPORT0 и SPORT1. Данные порты поддерживают множество последовательных протоколов обмена данными и, кроме того, обеспечивают прямое соединение процессоров в многопроцессорной системе. Рассмотрим подробнее эти устройства и команды, которыми они управляются.

Каждый SPORT имеет пять интерфейсных линий:

SCLK — тактовый сигнал;

RFS — прием кадровых синхроимпульсов;

TFS — передача кадровых синхроимпульсов;

DR — прием данных;

DT — передача данных.

SPORT1, в отличие от SPORT0, имеет возможность программно переназначать все сигнальные линии, кроме SCLK. Описание выводов последовательных портов сигнального процессора ADSP-2181 приведено в табл. 21.1.

Таблица 21.1 Описание выводов последовательных портов сигнального процессора ADSP-2181

| Сигнал | Направление | Назначение |

|---|---|---|

| DT0 | О | Передача данных |

| TFS0 | I/O | Кадровая синхронизация передачи |

| RFS0 | I/O | Кадровая синхронизация приема |

| DR0 | I | Прием данных |

| SCLK0 | I/O | Программируемый генератор порта 0 |

| DT1/FO | O | Передача данных или выходной флаг |

| TFS1/IRQ1 | I/O | Кадровая синхронизация передачи или внешний запрос прерывания 1 |

| RFS1/IRQ0 | I/O | Кадровая синхронизация приема или внешний запрос прерывания 0 |

| DR1/FI | I | Прием данных или входной флаг |

| SCLK1 | I/O | Программируемый генератор порта 1 |

I — вход, O — выход, I/O — вход/выход.

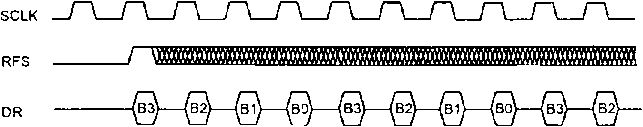

SPORT0 и SPORT1 способны одновременно принимать последовательный поток данных на входе DR и передавать последовательный поток через выход DT, обеспечивая тем самым дуплексный режим работы. Кроме того, передаваемые и принимаемые данные могут быть аппаратно запакованы и распакованы с помощью аппаратного блока компандирования. Данная процедура широко применяется в аппаратуре цифровой связи. Биты данных синхронизируются тактовыми синхроимпульсами SCLK внутреннего генератора, если процессор запрограммирован как источник синхронизации. Если порт запрограммирован в режим внешней синхронизации, SCLK становится входом для внешних импульсов синхронизации.

Сигналы кадровой синхронизации RFS и TFS используются для указания начала слова последовательно передаваемых данных или потока последовательно передаваемых слов. Эти сигналы также могут генерироваться внутри процессора или формироваться извне.

На рис. 21.1 показана структурная схема последовательного порта.

Рис. 21.1. Структурная схема последовательного порта

Данные, предназначенные для передачи, записываются через шину данных DMD из внутреннего регистра процессора в регистр данных передатчика порта TX. Эти данные могут перед передачей сжиматься в блоке компандирования (упаковки-распаковки) при задании такого режима. После чего данные автоматически передаются в сдвиговый регистр передатчика. Из регистра сдвига биты передаются на вывод последовательного порта DT, начиная со старшего разряда, синхронно с тактовыми синхроимпульсами SCLK. Приемник последовательного порта принимает данные с вывода DR, также синхронно с тактовыми синхроимпульсами SCLK. После приема одного слова данные распаковываются в блоке компандирования (если такая процедура была предварительно программно задана), а затем передаются в регистр данных приемника RX последовательного порта. Таким образом, происходит аппаратная одновременная передача и прием последовательных данных в обоих портах.

После записи данных в регистр TX последовательного порта этот порт готов к передаче данных. Передача начинается синхронно с сигналом TFS. После начала передачи каждое слово, записанное в регистр TX, подается во внутренний сдвиговый регистр передатчика, откуда оно передается на выход последовательно по битам, начиная с самого старшего бита. Каждый бит сдвигается по переднему фронту тактового синхроимпульса. После окончания передачи первого (самого старшего) бита слова последовательный порт генерирует прерывание передатчика. Несмотря на то, что передача первого слова продолжается, становится возможной запись нового слова данных в регистр TX.